International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified Vol. 5, Issue 10, October 2017

# Two Stage PFC Boost Doubler with Interleaved Control Scheme

K Iswarya Lakshmi<sup>1</sup>, M Shanthi<sup>2</sup>

Student, Department of EEE, Kamaraj College of Engineering and Technology, Virudhunagar, India<sup>1, 2</sup>

**Abstract**: A diode bridge with two power switches is employed as a PFC circuit to achieve a high power factor and low line current harmonic distortion. Interleaved Control Scheme (ICS) scheme with PI voltage controller and PI current controller is used to generate three-level PWM on the dc side of diode rectifier. Based on the control scheme, the line current is driven to follow the sinusoidal current command which is in phase with the supply voltage, and the output voltage is found to be balanced. At rated power, the source current THD value is less than 5% when PI as voltage and current controller in the ICS.

Keywords: ICS, THD, HCC, PWM, PI, Power Factor, Total Harmonic Distortion (THD), Dual boost converter, Boost doubler

## I. INTRODUCTION

Generally speaking, the PFC function includes shaping the current waveform and regulating the output voltage [1]. Due to the continuous input current, the boost-type converter has been widely integrated to the switch-mode rectifier (SMR) to achieve the desired PFC function [2]. The gate signal GT is obtained from the comparison of controller output signal  $v_{cs}$  and sawtooth signal. ICS includes an inner current loop and an outer voltage loop, and it is often used to generate the gate signal for the conventional boost-type SMR. One inductor current signal is fed back to the inner current loop to shape the current waveform. The output voltage is sensed for the outer voltage loop to regulate the output voltage. Sensing input voltage is also required for the generation of the desired current reference [3], [4] and the feedforward terms [5], [6]. In [7] and [8], some compensation loops are added to the multiloop control to improve the PFC performance for motor drive applications. For the boost converter, the single switch needs to withstand the overall output voltage when the switch blocks. The three-level boost converter is shown in Fig. 1 where two capacitors are connected across the switches, respectively. Thus, each switch needs to withstand only a half output voltage. In addition, the inductor voltage in the three-level boost converter has three levels, but the inductor voltage in the conventional boost converter has only two levels. Therefore, the three-level boost converter is able to yield smaller inductor current ripple than the conventional boost converter. It follows that three-level converters are often used in the applications, such as the high-voltage-ratio dc/dc conversion [9]-[12] and the wide input voltage range [13], particularly in the fuel cell applications [11], [13] and the grid-connected applications [10], [14], [15]. Additionally, the high-withstanding-voltage semiconductor switches often have larger drain-source resistances than the lowwithstanding-voltage ones. Thus, the three-level converter has the advantages of low voltage stress, small inductor current ripple, and low switching loss [1], [11], [16].

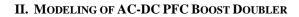

Fig. 1 Circuit configuration of single-phase AC-DC dual boost converter

# International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2017

Fig 1 shows the single phase AC-DC dual boost converter. This circuit strategy consists of a single phase diode bridge rectifier, two power switching devices, one inductor, two fast recovery diodes and two dc capacitors. An inductor  $L_b$  is used to reduce current ripple. The voltage rating of the power semiconductors are reduced to half of dc bus voltage. The inductor boost volume is one quarter of the conventional boost converter. The single phase three level rectifier can be analysed in its four operating modes according to the states of two power semiconductor switches  $M_1$  and  $M_2$ .

|      | =                        | -             |

|------|--------------------------|---------------|

| S.No | Parameter                | Specification |

| 1    | Input line voltage (Vs)  | 28 V          |

| 2    | Output voltage           | 48 V          |

| 3    | Output power             | 100 W         |

| 4    | Switching frequency (fs) | 20 kHz        |

| 6    | Line frequency           | 50 Hz         |

| 7    | Boost inductor (Lb)      | 3 mH          |

| 8    | Capacitance C1=C2        | 6000 µF       |

| 9    | Load resistance          | 23 Ω          |

Table 1 Design value of circuit components

Table 1 shows the design values of circuit components used in two stage AC-DC dual boost converter.

A. Interleaved Control Scheme (ICS)

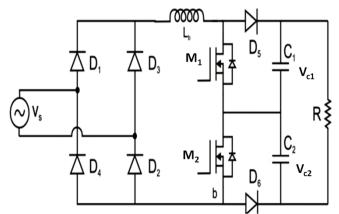

Fig. 2 Block diagram of Interleaved Control Scheme (ICS)

Fig 2 shows the Interleaved Control Scheme (ICS) block of the single phase AC-DC dual boost converter. It comprises of phase locked loop, conventional multi loop control with voltage controller and current controller, feed forward loop and interleaved PWM scheme. In outer voltage control loop, the converter output voltage is sensed and compared with the reference voltage. After comparison, error signal is fed to the voltage controller. The supply voltage is processed by the phase locked loop in order to produce absolute value of  $|sin\omega t|$ . The voltage controller output and absolute value of  $sin\omega t$  are used to obtain the amplitude of reference inductor current. This reference inductor current is compared with actual inductor current. After comparison, error signal is fed to the inner current control loop.

The comparator is used to compare the two ramp signals with the control signal generated,  $V_{cs.}$  Two gate signals are generated from the comparisons between the control signal  $V_{cs}$  and two sawtooth signals  $V_{t1}$  and  $V_{t2}$ .

These two sawtooth signals have equal amplitude and identical period  $T_s$  but there is 180 phase difference between them. The comparator produces the pulses for switches  $M_1$  and  $M_2$  when the control signal is greater than the ramp signals.

## B. Design of PI Controller

The PI controller takes into account the desired output of the converter to produce control signal which is necessary to reduce the error signal approximately to zero. A proportional controller gain  $(K_p)$  has the effect of reducing the rise time and does not eliminate the steady state error. An integral control gain  $(K_i)$  has the effect of eliminating the steady state error but makes the transient response worse. The error voltage obtained from the comparison of reference output voltage and actual output voltage is fed to the PI voltage controller in order to produce the peak value of input current.

An error signal, e(t) is used to control the switches in a converter. This error is the difference between the desired current,  $i_{ref}$ , and the current through the boost inductor,  $i_{act}$ . This error current is given to PI current controller. After processed by PI controller, The control signal  $v_{cs}$  is generated.

Copyright to IJIREEICE

#### DOI 10.17148/IJIREEICE.2017.51013

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2017

#### **III. SIMULATION OF THE SYSTEMS**

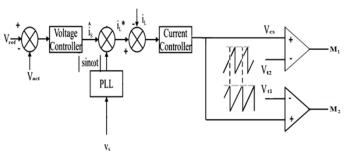

Fig. 3 Simulated circuit diagram of three level AC-DC converter with open loop control

Fig 3 shows the simulated circuit diagram of single phase AC-DC three level converter with open loop control.

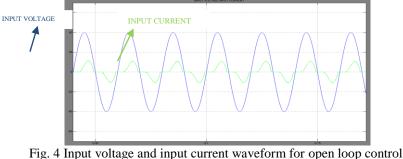

Fig 4 shows the input voltage and input current waveform with open loop control. This non sinusoidal input current is due to harmonic distortion in input current waveform.

|     |                    |   |   |   |    |  |  |     |   |  |     |  |  |  |     |  |  |   |    |  |  |  |     |  |  |    |  |  |  |    |   |  |  |   |   |  | l |

|-----|--------------------|---|---|---|----|--|--|-----|---|--|-----|--|--|--|-----|--|--|---|----|--|--|--|-----|--|--|----|--|--|--|----|---|--|--|---|---|--|---|

|     | $ \land$           |   |   |   | L  |  |  | Į., |   |  |     |  |  |  |     |  |  |   | Τ  |  |  |  | Į., |  |  |    |  |  |  | ļ  |   |  |  |   |   |  |   |

|     | 1                  |   |   |   | 1  |  |  | l   |   |  |     |  |  |  | L   |  |  |   | Т  |  |  |  |     |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

| 77  |                    |   |   |   | Т  |  |  |     |   |  |     |  |  |  | ſ.  |  |  |   | Τ. |  |  |  | T   |  |  |    |  |  |  | Т  |   |  |  |   |   |  |   |

| +   |                    |   |   |   | ÷  |  |  | in. |   |  | ŀ   |  |  |  |     |  |  |   | ÷  |  |  |  | ŀ   |  |  | ٠i |  |  |  | ÷  |   |  |  | h |   |  |   |

| L   |                    |   |   |   | 1. |  |  |     |   |  |     |  |  |  | ١., |  |  |   | 4  |  |  |  |     |  |  |    |  |  |  | .1 |   |  |  |   |   |  |   |

| í.  |                    |   |   |   |    |  |  |     |   |  |     |  |  |  |     |  |  |   | 1  |  |  |  |     |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

|     |                    |   |   |   | Ť  |  |  |     |   |  |     |  |  |  |     |  |  |   | Ť  |  |  |  | t   |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

|     |                    |   |   |   | i. |  |  | i.  | _ |  | i.  |  |  |  | ί.  |  |  | _ | i. |  |  |  | i.  |  |  | j  |  |  |  | j, |   |  |  |   | _ |  |   |

|     |                    |   |   |   | ÷  |  |  |     |   |  |     |  |  |  | ÷   |  |  |   | ÷  |  |  |  |     |  |  |    |  |  |  | 4  | - |  |  |   |   |  |   |

|     | $\mathbf{\Lambda}$ | Ś |   |   |    |  |  |     |   |  |     |  |  |  |     |  |  |   | 4  |  |  |  | L   |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

|     | Ł                  | ~ | _ | _ | 1  |  |  | 1   | _ |  |     |  |  |  | 1   |  |  | _ | 1  |  |  |  |     |  |  | _  |  |  |  | -  |   |  |  |   | _ |  |   |

|     |                    |   |   |   | ÷  |  |  | †-  |   |  |     |  |  |  | t   |  |  |   | ÷  |  |  |  |     |  |  | -1 |  |  |  | ÷  |   |  |  |   |   |  |   |

| - / |                    |   |   |   | 4. |  |  | ١., |   |  | Į., |  |  |  |     |  |  |   | 4  |  |  |  | l., |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

| 1   |                    |   |   |   |    |  |  |     |   |  |     |  |  |  |     |  |  |   |    |  |  |  |     |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

| 7   |                    |   |   |   | T  |  |  | T   |   |  |     |  |  |  | r   |  |  |   | Ť  |  |  |  |     |  |  | 1  |  |  |  | 1  |   |  |  |   |   |  |   |

| ł   |                    |   |   |   | ÷  |  |  | ÷   |   |  | ŀ   |  |  |  | ÷   |  |  |   | ÷  |  |  |  | ÷   |  |  |    |  |  |  | ÷  |   |  |  |   |   |  |   |

| L   |                    |   |   |   | 1  |  |  | 1   | _ |  | ί.  |  |  |  | i.  |  |  | _ | 1  |  |  |  | 1   |  |  | 1  |  |  |  | ÷  |   |  |  |   | _ |  |   |

|     |                    |   |   |   |    |  |  |     |   |  |     |  |  |  |     |  |  |   |    |  |  |  |     |  |  |    |  |  |  |    |   |  |  |   |   |  |   |

Fig. 5 Output current and output voltage waveform for open loop control

Fig 5 shows the output voltage and output current obtained from the open loop simulation of three level converter. The desired output voltage of 48V is not obtained in open loop control. Table 2 Open loop analysis

| Percentage of Load (%) | Output Voltage<br>(V) | Input Current THD<br>(%) | Power Factor |

|------------------------|-----------------------|--------------------------|--------------|

| 100                    | 43.5                  | 51.41                    | 0.7777       |

| 75                     | 44.94                 | 56.75                    | 0.7743       |

| 50                     | 46.72                 | 64.29                    | 0.7652       |

| 25                     | 49.17                 | 77.17                    | 0.7417       |

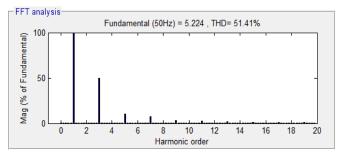

Table 2 shows the performance analysis of open loop control of single phase three level converter by varying the load resistance. for rated load, the total harmonic distortion of source current is very high and the value of THD obtained is 51.41%.

# International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2017

Fig. 6 FFT analysis for open loop control

Fig 6 shows the FFT analysis of total harmonic distortion with open loop control. By increasing load resistance, output voltage and THD are increased. But input power factor and efficiency are decreased. According to IEEE norms, harmonic should be less than 5%, which is not obtained in open loop control.

## IV. CLOSED LOOP ANALYSIS

Closed loop control is a feedback control that deals with the behavior of dynamical systems with inputs. The external input of a system is called the reference. When one or more output variables of a system need to follow a certain reference over time, a controller manipulates the inputs to a system to obtain the desired effect on the output of the system.

C. Single phase three level AC-DC converter with PI voltage controller and PI current controller

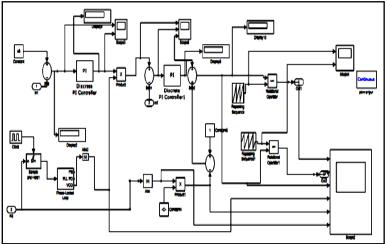

Fig. 7 Simulated circuit diagram of three level AC-DC converter with PI voltage controller and PI current controller

Fig 7 shows the simulated circuit diagram of proposed converter with PI controller. The proportional gain, integral gain values of PI controller is obtained from the transfer function of three level AC-DC converter with proper tuning. In PI control technique input current and output voltage are controlled by PI control.

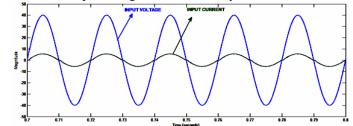

Fig. 8 Input voltage and input current waveforms for PI voltage controller and PI current controller

Fig 8 shows the input voltage and input current waveforms for proportional integral control. Input voltage and input current waveforms are in phase. Therefore input power factor is closed to unity. Input current waveform is slightly distorted.

Copyright to IJIREEICE

## International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2017

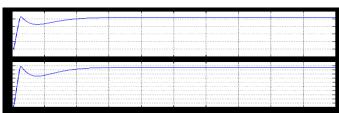

Fig. 9 Output current and output voltage waveforms for PI voltage controller and PI current controller

Fig 9 shows the output current and output voltage waveforms with PI voltage controller and PI current controller. From this waveform, the output voltage is maintained at 48V.

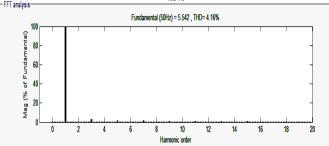

Fig. 10 FFT analysis for PI voltage controller and PI current controller

Fig 10 shows the FFT analysis of source current using PI voltage controller and PI current controller at rated load condition. Table 3 Closed loop analysis

| Percentage of Load<br>(%) | Output Voltage (V) | Input Current THD<br>(%) | Power Factor |

|---------------------------|--------------------|--------------------------|--------------|

| 100                       | 48                 | 4.16                     | 0.9990       |

| 75                        | 48                 | 4.98                     | 0.9986       |

| 50                        | 48                 | 5.82                     | 0.9977       |

| 25                        | 48                 | 7.41                     | 0.9963       |

# Table 3 shows the performance analysis of boost doubler for variation in loads. At rated load condition, source current total harmonic distortion is 4.16%. The input power factor becomes 0.9990 (i.e) nearly unity. By increasing the load resistance, source current harmonics also increases and output voltage is maintained constant.

## V. CONCLUSIONS

The Interleaved Control Scheme of single phase AC-DC PFC boost doubler was simulated with variation in load. It is noted that no voltage balancing loop, capacitor voltage sensing and feedforward loop are required in this proposed ICS. The simulation was done for the boost doubler with combinations of various controllers such as PI voltage controller and PI current controller. PI controller integrated ICS reduces the THD value to 4.16% without adding any filter on supply side and power factor closer to unity.

## REFERENCES

- B. Singh, B. N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, D. P. Kothari, (2003), A review of single-phase improved power quality AC-DC converters, IEEE Transactions on Industrial Electronics, Vol. 50, Issue 5, pp. 962–981.

- [2] P Shobana, N Geetha, J Gnanavadivel, (2012), Enhancement of power quality of AC-DC Boost converter with HCC and FLC-A comparative study, International Conference on Computing, Electronics and Electrical Technologies (ICCEET), pp 254-258.

- S. Moon, L. Corradini, D. Maksimovic, (2011), Autotuning of digitally controlled boost power factor correction rectifiers, IEEE Transactions on Power Electronics, Vol. 26, Issue 10, pp. 3006–3018.

- [4] A. El Aroudi, M. Orabi, R. Haroun, L. Martinez-Salamero, (2011), A symptotic slow-scale stability boundary of PFC AC-DC power converters: Theoretical prediction and experimental validation, IEEE Transactions on Industrial Electronics, Vol. 58, Issue 8, pp. 3448–3460.

- [5] M. Chen, J. Sun, (2006), Feedforward current control of boost single-phase PFC converters, IEEE Transactions on Power Electronics, Vol. 21, Issue 2, pp. 338–345.

# International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering

ISO 3297:2007 Certified

Vol. 5, Issue 10, October 2017

- [6] J Gnanavadivel, Vidhya Chellappa, N Senthil Kumar, (2011), Comparison of power quality improvement techniques in ac-dc Cuk converter, International Conference on Computer, Communication and Electrical Technology (ICCCET), pp 400-404.

- [7] H. C. Chang, C. M. Liaw, (2011), An integrated driving/charging switched reluctance motor drive using three-phase power module, IEEE Transactions on Industrial Electronics, Vol. 58, Issue 5, pp. 1763–1775.

- [8] J. Y. Chai, Y. H. Ho, Y. C. Chang, C. M. Liaw, (2008), On acoustic-noise reduction control using random switching technique for switch-mode rectifiers in PMSM drive, IEEE Transactions on Industrial Electronics, Vol. 55, Issue 3, pp. 1295–1309.

- [9] J Gnanavadivel, N Senthil Kumar, P Yogalakshmi, (2017), Comparative Study of PI, Fuzzy and Fuzzy tuned PI Controllers for Single-Phase AC-DC Three-Level Converter, Journal of Electrical Engineering & Technology, Vol. 12, Issue 6, pp. 78-90.

- [10] W. Li, X. He, (2011), Review of nonisolated high-step-up DC/DC converters in photovoltaic grid-connected applications, IEEE Transactions on Industrial Electronics, Vol. 58, Issue 4, pp. 1239–1250.

- [11] A. Shahin, M. Hinaje, J. P. Martin, S. Pierfederici, S. Rael, B. Davat, (2010), High voltage ratio DC-DC converter for fuel-cell applications, IEEE Transactions on Industrial Electronics, Vol. 57, Issue 12, pp. 3944–3955.

- [12] Ribeiro, A. J. M. Cardoso, C. Boccaletti, (2013), Fault-tolerant strategy for a photovoltaic DC-DC converter, IEEE Transactions on Power Electronics, Vol. 28, Issue 6, pp. 3008–3018.

- [13] M. H. Todorovic, L. Palma, N. Enjeti, (2008), Design of a wide input range DC-DC converter with a robust power control scheme suitable for fuel cell power conversion, IEEE Transactions on Industrial Electronics, Vol. 55, Issue 3, pp. 1247–1255.

- [14] J Gnanavadivel, N Senthil Kumar, P Yogalakshmi, (2016), Implementation of FPGA based three-level converter for LIED drive applications, Journal of Optoelectronics and Advanced Materials, Vol. 18, Issue 5-6, pp. 459-467.

- [15] J Gnanavadivel, N Senthil Kumai, CN Naga Priya, KS Krishna Veni, (2017), Investigation of Power Quality Improvement in Super Lift Luo Converter, International Journal of Power Electronics and Drive Systems, Vol. 8, Issue 3, pp. 1240-1250.

- [16] J Gnanavadivel, N Senthil Kumar, P Yogalakshmi, (2017), Fuzzy Controller based Power Quality Improvement in Three Level Converter with Multiloop Interleaved Control for Marine AC/DC Applications, Indian Journal of Geo Marine Sciences, Vol. 46, Issue 9, pp. 1908-1919.